الوصف

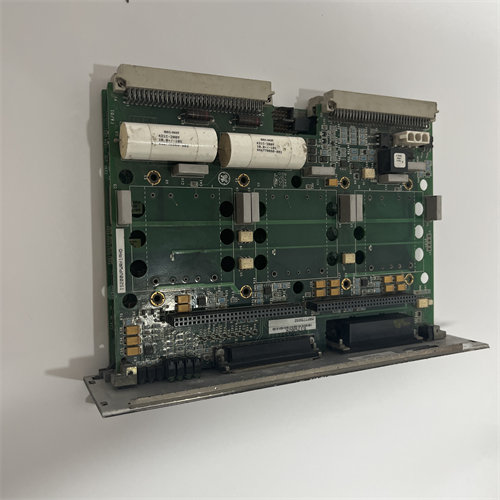

The GE DS200STCAG1ABA ARCNET LAN Driver Board, also known by its functional abbreviation STCA (Turbine Communication Board), is a vital component within the General Electric Mark V Speedtronic Turbine Control System.

It is not a simple terminal board but a complex processor card that functions as the primary data bridge and communication master for one of the control system’s redundant I/O cores. The ARCNET LAN Driver description refers to its role in managing communication across the system’s internal network.

Primary Functions in the Mark V System

The DS200STCAG1ABA board is typically mounted in a designated slot (e.g., on the LBC586P Board in the R core) and is responsible for integrating field data with the control processor. Each I/O core in the Mark V system requires an STCA board.

1. IONET Master & Data Processing

The STCA acts as the IONET (Input/Output Network) Master for its specific I/O core. This involves several critical tasks:

- Signal Acquisition & Conditioning: It receives raw or conditioned signals from other dedicated $\text{I/O}$ boards (like the TCQC) that monitor the turbine. These signals include pulse rate inputs (for shaft speed), generator, and bus voltage inputs. The STCA scales, filters, and conditions this data.

- Data Transfer: It writes the processed, clean data to the core’s I/O Engine (often located on an attached UCPB daughterboard) via bus connectors (P1 and P2).

2. Critical Turbine Control Logic

The board integrates specialized circuits to execute time-critical control and protection functions:

- Synch Check Circuit: It performs the synchronization check by processing voltage inputs. The results are used to calculate and initiate commands for the generator breaker synchronizing function, ensuring the generator is safely connected to the electrical grid.

- Pulse Rate Circuit: It accurately reads, scales, and conditions the high-pressure shaft pulse rate inputs from magnetic pickup devices, which is essential for precise speed control and overspeed protection logic.

3. ARCNET Network Interface

The “ARCNET LAN Driver” aspect highlights the board’s role in facilitating internal high-speed data exchange. It provides the physical and logical interface for the ARCNET data link, allowing data to be exchanged between the core processor, other communication boards (like the AAHA1 and AAHA2 via APL/BPL connectors), and the overall Mark V network.

Installation and Configuration

The DS200STCAG1ABA is a highly configurable board, requiring precise setup to match the specific turbine application:

| Feature | Detail |

| Location | Mounted on the $\text{LBC586P}$ processor board in the $\text{R}$ (Reference) core location. |

| Hardware Config | Features jumpers ($\text{JP2, JP4}$) to enable factory test points and select voltage for the flash EPROM. These settings must match the board being replaced. |

| Software Config | Requires configuration of I/O constants (e.g., pulse rates, synchronization settings, compressor stall logic) through the I/O Configuration Editor on the operator interface. |

In essence, the DS200STCAG1ABA is the sophisticated $\text{I/O}$ communications processor that manages the flow of critical turbine data, ensuring the high-speed, redundant control of the GE Speedtronic Mark V system functions reliably.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922