الوصف

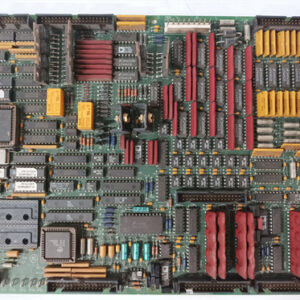

The GE DS200TCEAG2BTF is an Emergency Overspeed Board (Functional Acronym: TCEA) designed by General Electric for use in their Speedtronic Mark V Turbine Control Systems.1

This board is a critical safety component that operates within the protective core (2$P1$) of the Mark V panel to prevent catastrophic turbine failure.3

🛡️ Core Function and Role

The primary function of the DS200TCEAG2BTF is to provide high-speed protection for the turbine by monitoring critical safety parameters and initiating an emergency shutdown if necessary.4

- Overspeed Protection: It constantly monitors the rotational speed of the turbine shafts.5 If the speed exceeds a pre-configured trip threshold, it triggers an emergency trip signal to shut down the unit.6

- Flame Detection: The board also processes trip signals related to flame detection, which is crucial for gas turbine operation.7

- Protective Core Processor: It is often referred to as the Protective Processor because it is a key component of the triple-redundant safety logic in the Mark V system.8

🔄 Redundancy in the Mark V System

The Mark V system uses three identical TCEA boards (designated as X, Y, and Z processors) to ensure fail-safe operation. The DS200TCEAG2BTF is one of these boards.9

- Signal Processing: Each of the three TCEA boards independently receives and processes signals for high/low shaft speed and flame detection.10

- Voting Logic: The boards communicate the emergency trip signals to the Turbine Trip Board (TCTG).11 The TCTG then uses a 2-out-of-3 (2/3) voting logic to confirm a valid trip request before de-energizing the emergency trip relays and shutting down the turbine.12

🔧 Technical Details and Revisions

The full part number DS200TCEAG2BTF is a coded sequence that specifies the board’s function and its hardware/firmware revision level:

| Part Segment | Meaning | Value |

| DS200 | GE Drive System Series ($DS200$) | GE Mark V product series |

| TCEA | Turbine Control Emergency Alarm | Functional Acronym (Emergency Overspeed Board) |

| G | PCB Coating | Normal Coating |

| 2 | Functional Grouping/Release | Group 2 |

| B | Primary Functional Revision | Revision B |

| T | Secondary Functional Revision | Revision T |

| F | Artwork/Configuration Revision | Revision F |

Key Features:

- It typically contains an Intel 80196 microprocessor which executes the firmware and operating instructions stored in PROM/EPROM modules.13

- It includes hardware configuration jumpers used to set parameters like the IONET address and confirm the overspeed trip frequency settings.14

- The board communicates data to the Control Engine via the IONET network.15

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922