الوصف

That’s an excellent request! The GE DS200UCIBG1A is a fundamental component of a large-scale industrial control system.1

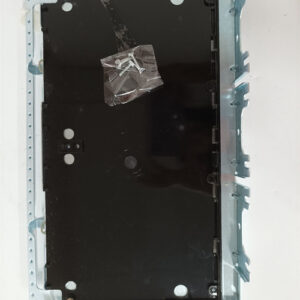

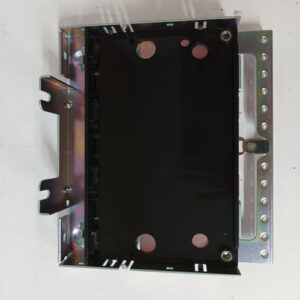

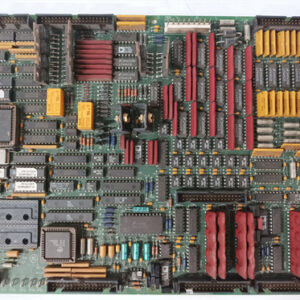

The DS200UCIBG1A is the UC2000 Motherboard for the R Core of the GE Mark V Speedtronic Turbine Control System.2

⚙️ Primary Function

The DS200UCIBG1A (UCIB) acts as the central mechanical and electrical interface for the turbine’s control engine. It is the board into which the primary control logic and communication boards are plugged.3

1. Host for Critical Daughterboards

The motherboard’s main function is to provide the connectors and bus structure for the following key control modules, which mount directly onto it:

- LBC586P Daughterboard: This is the actual Central Processing Unit (CPU) board, often containing a Pentium-class processor, that executes the turbine’s control sequencing and application software.

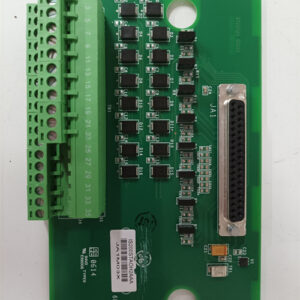

- PANA Board (ARCNET No-LAN Driver): This board is essential for the Triple Modular Redundancy (TMR) architecture of the Mark V. It handles the high-speed ARCNET network communication, allowing the three control cores (T, R, and S) to exchange vital data and vote on control signals.

- $\mu$GENI Boards: The UCIB provides connections for up to two $\mu$GENI (Micro Genius I/O) boards, which manage the interface with Genius I/O devices in the field.

2. Signal Pre-Processing

The UCIB board itself contains an onboard 196 microprocessor. This dedicated processor is responsible for an initial critical task:

- It translates high-resolution pressure transducer signals received from the TCSA board (Fuel Skid Interface Board), specifically for systems using Dry Low Emissions (DLE) technology.

- The translated, conditioned data is then written to the main LBC586P processor to be used in the final control algorithms.

🏷️ Part Number Breakdown

The structure of the part number is standard for GE Mark V boards and conveys specific characteristics:

| Part Segment | Detail | Meaning |

| DS200 | Series | Mark V Speedtronic Control System. |

| UCIB | Functional Acronym | UC2000 Core Mother Board (The ‘B’ often indicates a different physical connector/design standard than ‘UCIA’). |

| G1 | Grouping | Group 1 Mark V Series product grouping. |

| A | Revision | First functional revision of the base G1 design. |

In summary, the DS200UCIBG1A is the central nervous system backplane for one of the three redundant control cores in a GE gas turbine control panel.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922