الوصف

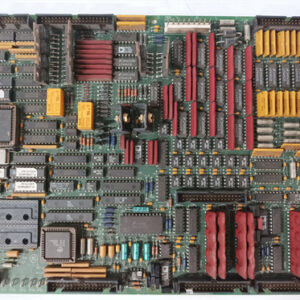

The GE DS200UCIBG1AAB is a UC2000 Motherboard designed for the R Core of the General Electric Mark V Speedtronic Turbine Control System.

This board is a critical component that acts as the primary backplane and interface for the main processing elements in one of the three redundant control cores (T, R, and S) used to manage industrial gas and steam turbines.

🔍 Function of the DS200UCIBG1AAB

The core function of the DS200UCIBG1AAB (UCIB) is to house and connect the specialized daughterboards that perform the main control logic and communication. It essentially acts as the central hub of the R Core.

1. Host for Processing Boards

The motherboard provides dedicated connectors for mounting the primary control components:

- CPU Board: It hosts the LBC586P (or similar) daughterboard, which contains the main industrial-grade CPU (like a Pentium processor) that executes the complex control algorithms, sequencing, and application code for the turbine.

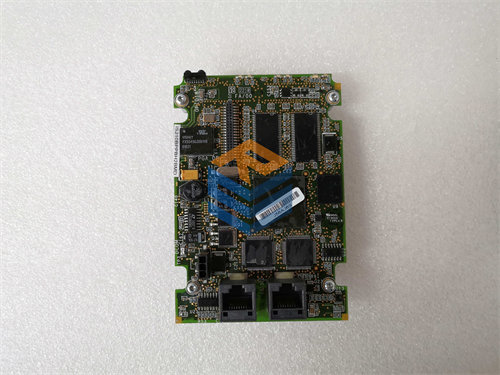

- ARCNET Communication Board: It hosts the PANA (ARCNET No-LAN Driver) board.1 This is vital for the Triple Modular Redundancy (TMR) architecture, enabling high-speed communication and data exchange among the three redundant cores (T, R, and S) for fault tolerance and signal voting.

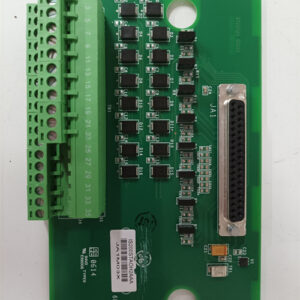

- I/O Interface Boards: It includes connections for up to two 2$\mu$GENI (Micro Genius I/O) boards, which manage the interface with I/O devices in the field.3

2. Signal Conditioning and Pre-Processing

The UCIB board contains its own onboard microprocessor (typically an Intel 80196) to handle high-priority, dedicated tasks:

- It translates raw data, such as high-resolution pressure transducer signals received from the TCSA board (Fuel Skid Interface Board), especially for systems with Dry Low Emissions (DLE) technology.4

- This conditioned data is then passed to the main CPU board (LBC586P) for integration into the larger control program.

📝 Part Number Interpretation

The extended part number DS200UCIBG1AAB provides a detailed manufacturing history and specific board configuration:

| Segment | Detail | Meaning |

| DS200 | Series | GE Mark V Speedtronic Control System. |

| UCIB | Functional Acronym | UC2000 Core Mother Board. |

| G1 | Grouping | Group 1 Mark V product grouping (indicates application context). |

| A | Primary Revision | The first functional revision of the board design. |

| AAB | Manufacturing/Coating Code | This often indicates subsequent manufacturing revisions, assembly code, or the type of protective coating applied to the board (e.g., standard or conformal coating for harsh environments). These trailing letters signify minor changes from the base part (DS200UCIBG1A). |

In short, the DS200UCIBG1AAB is the main foundation of the R Core logic in the Mark V control system, ensuring the reliability and redundancy that is critical for managing gas and steam turbines.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922