الوصف

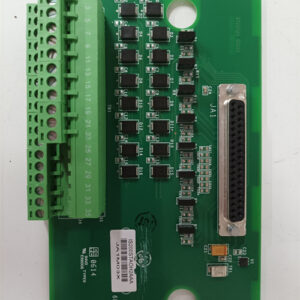

The GE DS200UCIBG3A is the UC2000 Motherboard for the R Core of the General Electric Mark V Speedtronic Turbine Control System ⚙️.1

This board is the foundational component that makes the complex control logic possible. The ‘G3A’ simply indicates that it is the Group 3 version with the first functional revision (‘A’).

🏗️ Core Function and Role

The DS200UCIBG3A doesn’t perform the main control calculations itself, but acts as the central backplane and electrical/mechanical interface for the core processing boards. It is housed in the ‘R’ core cabinet, which is one of the three redundant control engines ($T$, $R$, and $S$) that enable the Mark V system’s Triple Modular Redundancy (TMR).

1. Host for Critical Daughterboards

The motherboard features several high-density connectors for plugging in the main control modules:

- CPU Board: It hosts the LBC586P (or similar) daughterboard, which contains the main industrial-grade CPU (often a Pentium-class processor) responsible for executing the turbine’s control application code and sequencing.

- ARCNET Communication Board: It hosts the PANA board (ARCNET No-LAN Driver).2 This board is vital for the TMR architecture, allowing the three control cores to communicate and vote on control signals over a high-speed, redundant ARCNET network.

- I/O Adapters: It provides connections for $\mu$GENI (Micro Genius I/O) boards, which manage the interface with Genius I/O field devices.

2. Signal Pre-Processing

The UCIB board has its own onboard 80196 microprocessor. This dedicated processor handles time-critical, front-end tasks:

- It translates and conditions raw data, most notably high-resolution pressure transducer signals received from the TCSA board (Fuel Skid Interface Board).

- This pre-processed data is then passed to the main CPU board (LBC586P) to be used in the high-level control algorithms, particularly important for systems with Dry Low Emissions (DLE) technology.

🔢 Part Number Detail

| Segment | Detail | Meaning |

| DS200 | Series | Mark V Speedtronic Control System. |

| UCIB | Functional Acronym | UC2000 Core Mother Board. |

| G3 | Grouping | Group 3 designation, implying a specific variant of the Mark V hardware or generation. |

| A | Revision | The first functional revision of the G3 design. |

The DS200UCIBG3A is essential because it integrates the processing power, redundant communication, and I/O networking required for reliable, fault-tolerant turbine operation.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922