الوصف

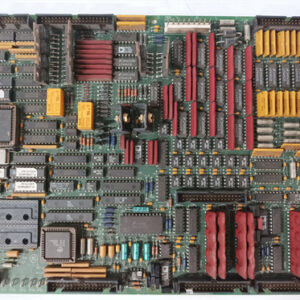

The GE DS200UCPBG5ADA is a critical component in the General Electric Mark V Speedtronic Turbine Control System.1 It is the I/O Engine Central Processing Unit (CPU) Board.

🚀 Primary Function: The Core Processor

The UCPB (UC2000 Processor Board) is the brain of the Input/Output (I/O) section within the control cores (2$R1, R2, R3$, and 3$R5$ I/O engines).4 Its main functions are to execute control algorithms, manage I/O data, and facilitate communication for the Triple Modular Redundancy (TMR) system.

1. Processing and Execution

- CPU: The board contains the main control processor, typically a 486-class (80486DX) or similar industrial-grade CPU, responsible for running the turbine’s sequence and protection algorithms.5

- Memory: It utilizes memory modules, such as SIMM (Single Inline Memory Module) sockets for DRAM (Dynamic RAM) and EPROM (Flash Erasable PROM) to store the operating system, firmware, and application software.6

2. Data Management and Communication

- I/O Packaging: The processor packages all the acquired analog and digital I/O data from the various field devices.7

- COREBUS Broadcast: It broadcasts this packaged data onto the COREBUS (via an onboard ARCNET driver) for use by the main T, R, and S control cores.8

- Fast Packets: Critical, high-priority data is broadcast at a high rate (e.g., 9$100 \text{ Hz}$ or every 10$10 \text{ ms}$).11

- Slow Packets: Less critical information is broadcast at a slower rate.

- I/O Configuration: It stores and loads the I/O configuration data for the respective I/O engine, ensuring correct mapping and scaling of signals.12

3. Physical Interface

The UCPB is a daughterboard that plugs directly into a mother board, such as the DS200UCIBG3AAB, which provides the connectors to the rest of the control circuitry.13

🔢 Part Number Breakdown

The specific part number DS200UCPBG5ADA provides detailed information about its generation and revision:

| Segment | Detail | Meaning |

| DS200 | Series | GE Mark V Speedtronic Control System. |

| UCPB | Functional Acronym | UC2000 Processor Board (I/O Engine CPU Board). |

| G5 | Grouping | Group 5 variant of the Mark V hardware, indicating a specific generation. |

| ADA | Revisions | First functional revision (A), second functional revision (D), and a production/artwork revision (A). |

The G5 designation places this board within a specific hardware grouping of the Mark V system, differentiating it from G4 or G6 versions that might use slightly different processors, memory configurations, or I/O interfacing schemes.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922