الوصف

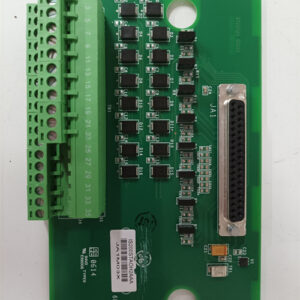

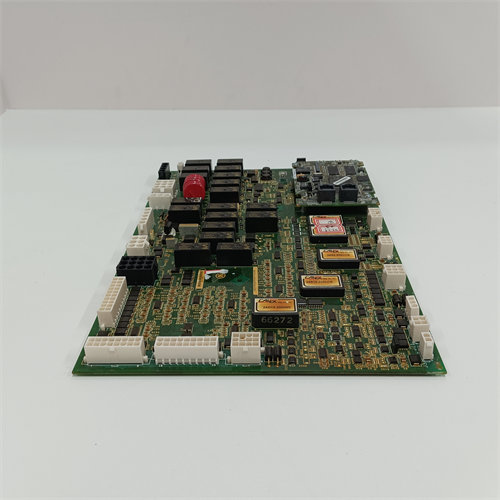

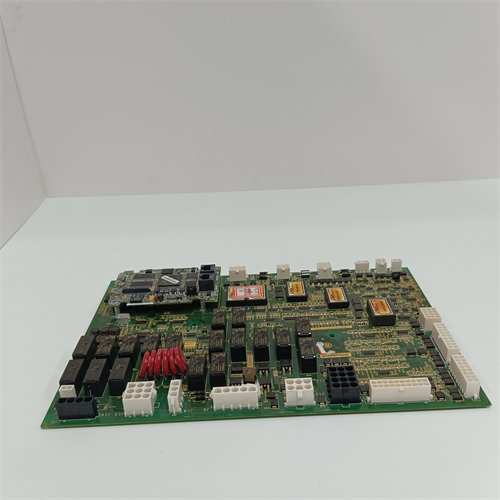

The GE part number DS200UCPBG5AFA is an I/O Engine CPU Board (Central Processing Unit) used in the GE Speedtronic Mark V Gas and Steam Turbine Control System.

The description “Turbine Power Connect Board” is inaccurate; the board’s primary function is processing and communications, not solely power connection.

⚙️ Function and Role in the Mark V System

The DS200UCPBG5AFA (UCPB) serves as the I/O Engine Processor, a critical component responsible for collecting and broadcasting field data to the main turbine controllers.

- I/O Data Acquisition: The board is mounted within one of the I/O sections of the control panel, where it collects analog and digital signals from the various I/O termination boards (which connect to the physical sensors and devices on the turbine).

- Data Processing: It includes a microprocessor (typically an 80486DX CPU) that processes, scales, and packages this raw input data.1

- COREBUS Communication: The processed I/O data is then broadcast over the high-speed COREBUS (an ARCNET LAN) network.2 This is how the main, triple-redundant $\text{R, S, T}$ control processors receive all the necessary data to execute the turbine’s control and protection logic.

- Daughtercard Design: It is designed as a daughtercard that plugs into a larger motherboard (like the 3$\text{UCIB}$ or 4$\text{STCA}$ board) within the I/O engine cabinet.5

This architecture distributes the processing load and allows the main control cores to focus on the high-speed triple-redundant $(\text{TMR})$ control loops, while the UCPB handles the I/O communication tasks.

🛠️ Key Technical Features

| Feature | Detail |

| System | GE Speedtronic Mark V Turbine Control System |

| Functional Acronym | $\text{UCPB}$ (UC2000 Processor Board) |

| Board Type | I/O Engine CPU Board / Processor Card |

| Processor | Typically an 80486DX (486-class) CPU |

| Memory | Includes a socket for $\text{SIMM}$ (Single Inline Memory Module) $\text{DRAM}$ and $\text{EPROM}$ (for firmware) |

| Communications | Built-in ARCNET driver for broadcasting data over the COREBUS to the R, S, T control cores |

The revision suffix G5AFA indicates the board’s specific hardware and firmware version within the $\text{DS200}$ series.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922