الوصف

The GE DS200UCPBG5AFB is a critical component known as the I/O Engine CPU Board (Input/Output Engine Central Processing Unit Board) for the General Electric Speedtronic Mark V Gas and Steam Turbine Control System.

This board’s main function is to handle the acquisition, processing, and communication of field data for the turbine’s main controllers.1

💻 Key Function of the UCPB Board

The DS200UCPBG5AFB (UCPB) acts as a specialized processor that offloads the routine I/O processing from the main, redundant control processors ($\text{R, S, T}$).

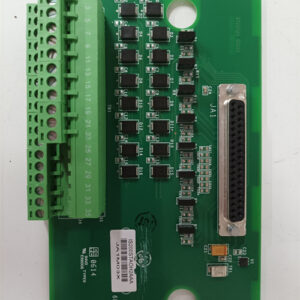

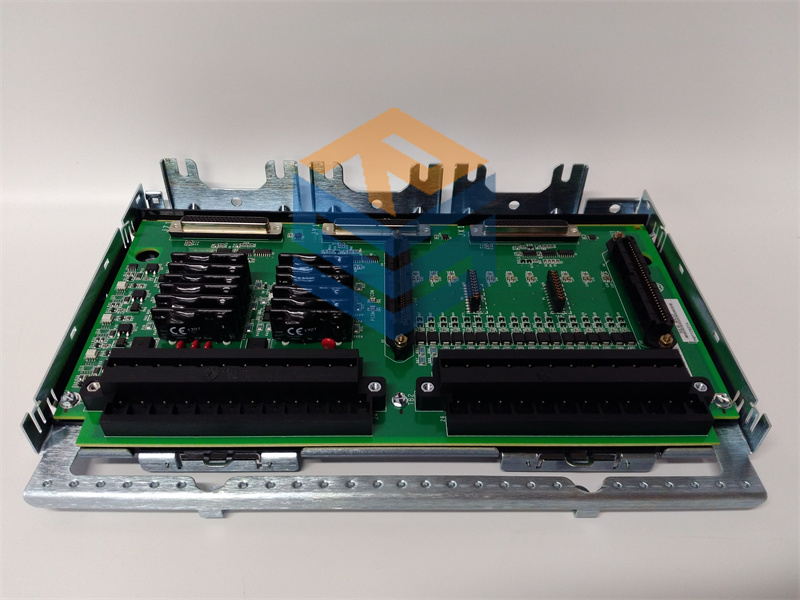

- I/O Data Acquisition: It is installed within one of the I/O Engine cores of the Mark V control panel, typically as a daughtercard mounted on a larger board like the 2$\text{STCA}$.3 Its role is to read the raw input signals (both analog and digital) that have been terminated by the I/O termination boards (like $\text{DTBA}$ or $\text{TBQA}$).

- Data Processing and Packaging: The on-board processor (4$\text{CPU}$), typically an 80486DX, processes and packages this I/O information.5

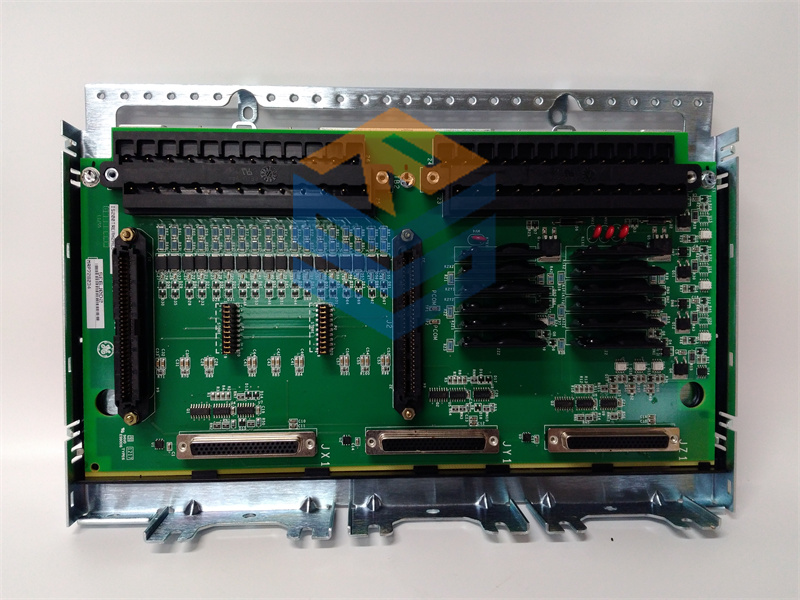

- COREBUS Communication: The processed data is then broadcast over the high-speed COREBUS (an 6$\text{ARCNET}$ LAN) network.7 This allows the main control cores ($\text{R, S, T}$) to receive the updated field values needed for the turbine’s control and protection logic.

- Configuration: The board contains 8$\text{DRAM}$ and 9$\text{EPROM}$ for memory and firmware.10 It also includes DIP switches and jumpers used to set the 11$\text{COREBUS}$ address for the specific I/O Engine it resides in, ensuring proper communication within the redundant system.12

In short, the UCPB board is the microprocessor interface that links the physical turbine sensors and actuators to the digital brains of the $\text{Mark V}$ control system.

📋 General Specifications

| Specification | Detail |

| Manufacturer | General Electric (GE) |

| Product Series | Speedtronic Mark V Turbine Control System ($\text{DS200}$ series) |

| Product Type | I/O Engine CPU Board / Processor Card |

| CPU | 80486DX (Typical) |

| Connectivity | $\text{ARCNET}$ driver for $\text{COREBUS}$, $\text{RS-232}$ serial ports, and $\text{J1/J2}$ bus connectors. |

| Installation | Daughtercard, often mounted on an $\text{STCA}$ (I/O Engine $\text{ST}$ Card Assembly) board. |

| I/O Engine Cores | A UCPB board is typically installed in each of the $\text{I/O}$ Engines ($\text{R1}$, $\text{R2}$, $\text{R3}$, etc.) to provide local processing power. |

The DS200 prefix signifies that this board belongs to the $\text{DS200}$ product series, which is a collection of circuit boards and components used in the $\text{Mark V}$ control system.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922