الوصف

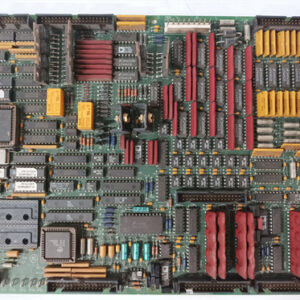

The GE DS200UCPBG5AFB I/O Engine CPU Board is a printed circuit board (PCB) manufactured by General Electric (GE) for use in their Mark V Speedtronic Turbine Control Systems.

It functions as an I/O Engine Central Processing Unit Board (UCPB), making it a critical component for managing control and data processing tasks within the Mark V system’s Input/Output (I/O) section.

⚙️ Key Specifications and Features

This board is typically a daughterboard that mounts onto a main board (like the STCA board) in one of the I/O Engine cores of the control system.

- Manufacturer: General Electric (GE)

- Series: Mark V Speedtronic Turbine Control Systems

- Product Type: I/O Engine CPU Board (UCPB)

- Application: Used for industrial control, particularly in turbine control systems.

🧩 Components and Functionality

- Processor: It features a microprocessor (in related revisions, this is an 80486DX processor).

- Memory: It includes provisions for memory, such as a dual in-line memory module (DIMM) connector and multiple PROM modules (Programmable Read-Only Memory) that store the firmware and programming instructions.

- I/O Management: Its primary role is to package analog and digital I/O information from various sensors and actuators and broadcast it onto the COREBUS. This enables communication with the main control system.

- Communication: It contains connectors for various communication and bus interfaces, which may include:

- An ARCNET driver for network communication.

- COM1 and COM2 serial ports (RS-232).

- J1 and J3 Bus Connectors.

- Configuration: The board often has hardware jumpers and/or DIP switches for setting configurations like the COREBUS address for the specific I/O Engine.

🏭 System Context (Mark V)

In the GE Mark V system, the control is handled by a triple-redundant architecture (R, S, and T cores). The UCPB board is part of the I/O Engines (often designated R1, R2, R3, R5, etc.) that interface the core controllers with the physical plant I/O (sensors and actuators).

The I/O Engine CPU Board is essential for:

- Reading: Collecting data from connected I/O boards.

- Processing: Executing local control and diagnostic functions.

- Communication: Transmitting processed I/O data to the main control cores via the COREBUS in “fast packets” (for critical data) and “slow packets” (for less critical data).

This component is typically found in older, but still functional, industrial installations and is generally classified as a discontinued/legacy product that is supported via surplus or repair services.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922