الوصف

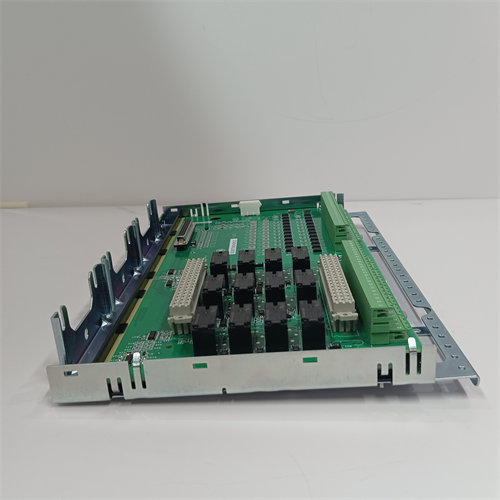

The GE DS200UCPBG6ADA I/O Engine CPU Board is an Input/Output Engine Central Processing Unit Board (UCPB) manufactured by General Electric for their Mark V Speedtronic Turbine Control Systems.

This board is a critical processing and communication component that manages the flow of data between the turbine’s sensors and actuators (the I/O) and the main, triple-redundant control processors (R, S, and T cores).1

🧠 Key Specifications and Function

The 2$\text{DS200UCPBG6ADA}$ is one of the various revision levels of the 3$\text{UCPB}$ board (4$\text{DS200UCPBG6A}$ is the base part number).5 It acts as the brain for one of the 6$\text{I/O}$ Engine cores (R1, R2, R3, or R5).7

- Primary Function: To collect, process, and package analog and digital 8$\text{I/O}$ data from the local boards (like sensor and actuator interfaces) within its engine core.9

- Processor: It contains a microprocessor, typically an 80486DX CPU, to execute the local control and diagnostic firmware.

- Communication: It broadcasts the processed 10$\text{I/O}$ information to the main control cores using an ARCNET driver over the COREBUS.11

- Fast Packets: Critical, high-priority data is transmitted at a rate of 12$100\text{ Hz}$ (every 13$10\text{ ms}$).14

- Slow Packets: Less critical data is sent at a slower rate.15

- Mounting: It is a daughterboard that plugs into a main carrier board, such as the 16$\text{STCA}$ board, within the 17$\text{I/O}$ engine section of the Mark V panel.18

🛠️ Configuration and Replacement Notes

When handling or replacing this board, several key hardware components are critical for maintaining system function:

- PROM Modules: The board contains sockets for Programmable Read-Only Memory (PROM) modules.19 These modules hold the firmware and programming instructions unique to the system’s configuration.20 The PROMs must be carefully removed from the old board and transferred to the new board to ensure the new CPU board operates with the correct turbine programming.21

- COREBUS Address: The board features DIP switches that are used to set the unique COREBUS address for the specific 22$\text{I/O}$ Engine it is installed in (e.g., setting it as 23$\text{R1}$, 24$\text{R2}$, etc.). The switch settings must match the configuration of the board it is replacing.25

- Connectors: Key connectors include $\text{ARCNET}$ (for COREBUS connection), $\text{COM1}$ (for the Terminal Interface Monitor/RS-232), $\text{COM2}$, and bus connectors $\text{J1}$ and $\text{J3}$ for interfacing with the main carrier board.

The $\text{DS200UCPBG6ADA}$ is an older, legacy component for the industrial control market and is primarily supported through repair or surplus parts channels.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922