الوصف

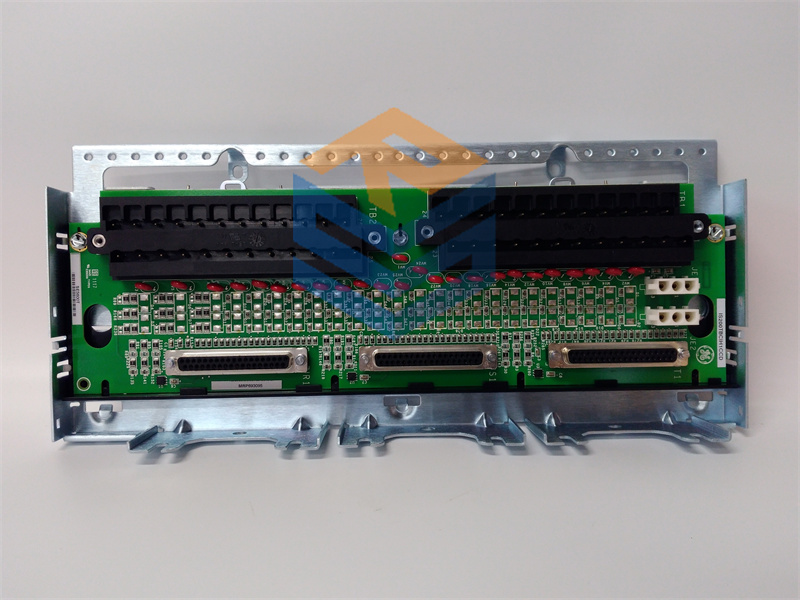

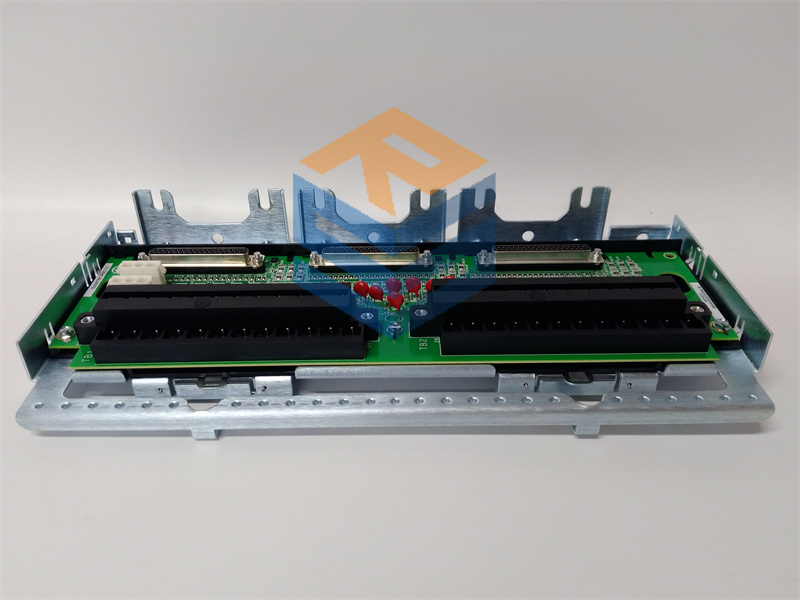

The GE DS200UCPBG7AHB is an I/O Engine CPU Board (UCPB) designed by General Electric for the Speedtronic Mark V Turbine Control System.

It functions as the dedicated central processing unit for an Input/Output ($\text{I/O}$) engine, managing the collection, processing, and communication of field device data (sensors and actuators) to the main turbine controllers.

🚀 Key Specifications

The DS200UCPBG7AHB is a high-specification variant of the 1$\text{UCPB}$ series within the Mark V system, part of the Group 7 series components.2

| Feature | Detail |

| System Series | GE Speedtronic Mark V |

| Functional Acronym | UCPB (I/O Engine CPU Board) |

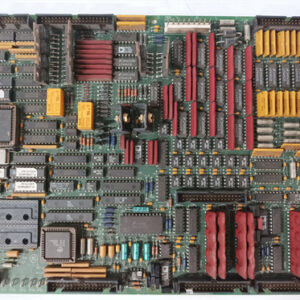

| Processor | 486DX4-100 processor |

| Memory | 8M DRAM (Dynamic Random Access Memory) / 4M FLASH memory |

| Primary Function | Processes, packages, and transmits analog and digital I/O data. |

| Location | Installs as a daughterboard on the $\text{STCA}$ board within an I/O core ($\text{R1}$, $\text{R2}$, $\text{R3}$, or $\text{R5}$). |

| Communication | Uses an ARCNET driver to communicate via the COREBUS to the main $\text{R, S, T}$ control cores. |

⚙️ Role in the Control System

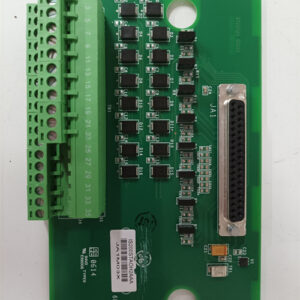

- Distributed Processing: The $\text{UCPB}$ offloads I/O data processing from the main $\text{R, S, T}$ controllers. It digitizes, scales, and prepares signals from I/O terminal boards.

- Data Transmission: It packages the processed I/O data into high-speed “fast packets” (for critical signals) and “slow packets” and broadcasts them over the 3$\text{COREBUS}$ using the ARCNET protocol.4

- Corebus Address: The board contains DIP switches to set its unique COREBUS address, which identifies the specific 5$\text{I/O Engine}$ it controls within the system.6

- Configuration Storage: The integrated $\text{FLASH}$ memory stores essential information, including the $\text{I/O}$ configuration data, which is loaded into the $\text{DRAM}$ upon reboot.

This board’s powerful processor and memory for its generation (7$\text{486DX4-100}$ with 8$8 \text{M DRAM}/4 \text{M FLASH}$) make it a robust solution for enhancing performance in the Mark V’s distributed control architecture.9

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922