الوصف

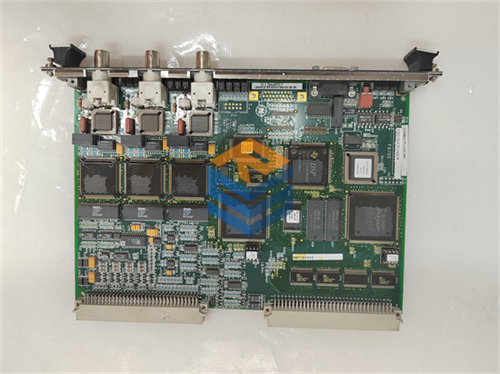

The GE DS200UCPBG7AHB I/O Engine CPU Board is an advanced revision of the Universal Control Processor Board (UCPB) designed for the General Electric Mark V Speedtronic Turbine Control System.

This board is the central processing unit for an Input/Output (I/O) Engine core, making it essential for processing and managing the data flow between the physical turbine I/O (sensors, actuators) and the main control system.

🚀 Key Technical Specifications

The G7AHB revision includes significant hardware upgrades compared to earlier revisions (G5 and G6 series), which enhanced processing power and memory:

- Functional Acronym: UCPB (Universal Control Processor Board).

- Processor: Features a 486DX4-100 processor (a faster variant of the 486 family).

- Memory: Includes a substantial amount of on-board memory:

- DRAM (Dynamic Random Access Memory): 8M

- FLASH Memory: 4M (used for storing the operating system and non-critical data).

- Application: Mounted as a daughterboard in one of the Mark V system’s I/O Engine cores (e.g., R1, R2, R3, R5).

⚙️ Core Functionality

The DS200UCPBG7AHB executes the critical control and communication tasks within its assigned I/O engine:

- I/O Data Packaging: It processes raw analog and digital signals collected from the surrounding I/O terminal boards.

- COREBUS Communication: It packages this processed information into data packets for transmission over the ARCNET COREBUS to the three main control cores (R, S, and T) to support the triple-redundant control logic.

- Critical data is sent in “fast packets” (e.g., at 100 Hz).

- Less critical data is sent in “slow packets”.

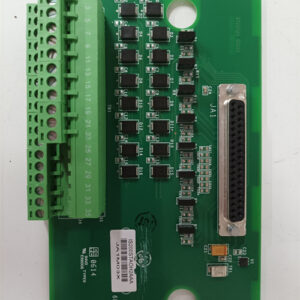

- Firmware Storage: Like its predecessors, it includes sockets for PROM (Programmable Read-Only Memory) modules which hold the system’s turbine-specific firmware and programming instructions.

📝 Installation Notes

When replacing this board, it is vital to transfer the following components and settings from the old board to the new board to maintain the turbine’s configured operational logic:

- PROM Modules: The firmware PROMs must be physically transferred to the corresponding sockets on the replacement board.

- DIP Switches: The DIP switches used to set the COREBUS address for the I/O Engine must be set exactly as they were on the original board.

The DS200UCPBG7AHB is part of GE’s Mark V product line, which is generally considered a legacy system, and support is typically provided through specialized repair and surplus channels.

+86 15340683922

+86 15340683922 +86 15340683922

+86 15340683922